# **Microcontroller Basics**

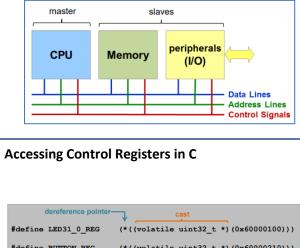

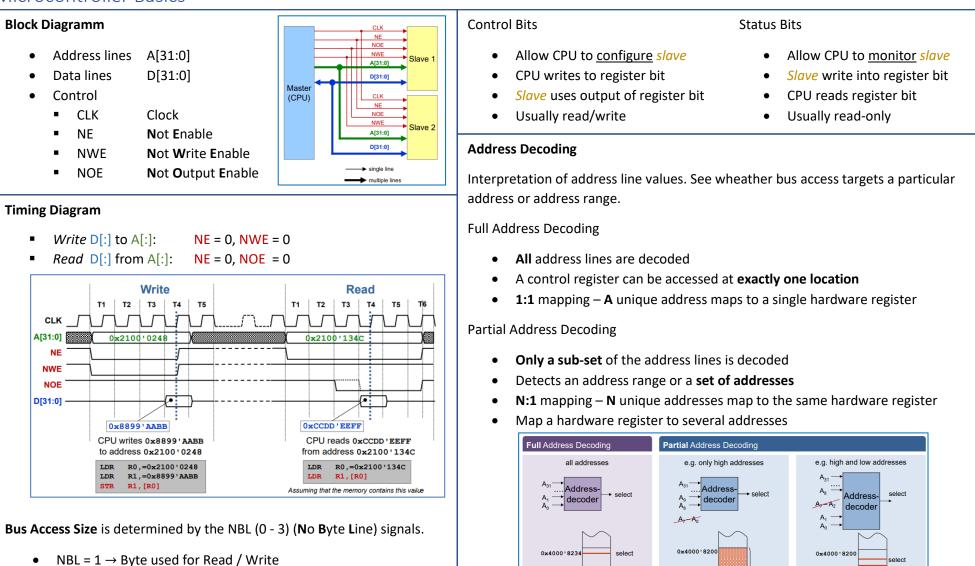

### Signal Groups

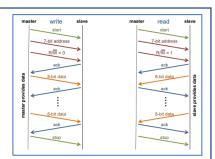

### **Data lines**

- 8, 16, 32, 64 parallel lines of data

- Bidirectional (read / write)

## **Address lines**

- Unidirectional: From master to slave

- Number of lines  $\rightarrow$  size of address space

## **Control signals**

- Control read / write direction

- Provide timing information

# dereference pointer #define LED31\_0\_REG (\*((volatile uint32\_t \*) (0x60000100))) #define BUTTON\_REG (\*((volatile uint32\_t \*) (0x60000210))) // Write LED register to 0xBBCC'DDEE LED31\_0\_REG = 0xBBCCDDEE; // Read button register to aux\_var aux\_var = BUTTON\_REG;

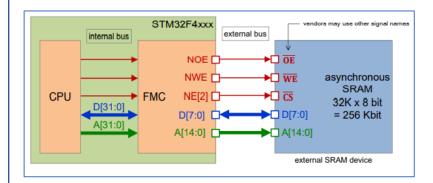

## **Timing Options**

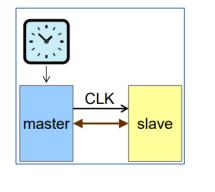

# <u>Synchronous</u>

- Master and slave use a common clock

- Clock edges control bus transfer on both sides

- Used by most on-chip busses

- Off-chip: DDR and synchronous RAM

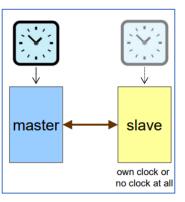

## <u>Asynchronous</u>

- *Slaves* have no access to the clock of the master

- Control signals carry timing information to allow synchronization

- Widely used for low data-rate off-chip memories

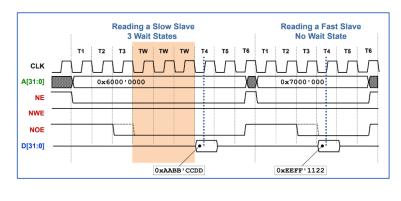

# **Slow Slaves**

• Wait states are inserted depending on the address of an access

# **Microcontroller Basics**

- NBL[0:3] = 0011  $\rightarrow$  Read Half-Word

- NBL[0:3] = 0010  $\rightarrow$  Read Byte

selec

0x4000'82FF

0x4000'82FF

# GPIO - General Purpose Input / Output

## Register address = Base address + Offset

- Offset is given for each register in reference manual ٠

- Base address defined in memory map (reference manual)

## GPIO

### Situation

- Microcontroller as general-purpose device

- Many functional blocks included

#### Problem

- Limited number of pins

- For a specific configuration, not all functions can be routed to I/O pins

Boundary address

4002 2800 0x4002 2BEE

002 2400 - 0x4002 27F

4002 2000 - 0x4002 23FF

x4002 1C00 - 0x4002 1FFI

4002 1800 - 0x4002 1BF

x4002 1400 - 0x4002 17FF

x4002 1000 - 0x4002 13FF

x4002 0C00 - 0x4002 0FFF

0x4002 0800 - 0x4002 0BFF

4002 0400 - 0x4002 07FF

4002 0000 - 0x4002 03FF

Peripheral

GPIOK

GPIO.I

GPIOI

GPIOH

GPIOG

GPIOF

GPIOE

GPIOD

GPIOC

GPIOB

GPIOA

### Solution

- Many (all) pings are configurable

- Select the needed I/O pins / functions

- «pin sharing»

- Output multiplexer needs to be configured •

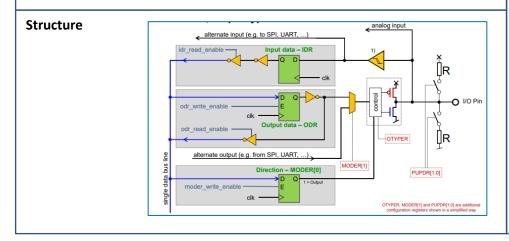

## **Configuration Registers**

- GPIOx MODER[1:0] Direction

- GPIOx OTYPER[0:0]

- Output type

- Push-Pull / Open-Drain (Low)

- GPIOx PUPDR[1:0] Pull-Up / Pull-Down

- GPIOx OSPEEDR[1:0] Speed

- Low, Medium, ...

e.g. Input, Analog mode, ...

# Setting and Clearing Bits - GPIOx\_BSRR

- Set port bit by writing a '1' to BSRR[bit] • 0-15 Set Bits

- Clear port bit by writing a '1' to BSRR[bit+16] 16-31 Clear Bits

- Ensures atomic access in software (no interruption possible) •

### **Data operations**

- Read register GPIOx IDR Input

- Write register GPIOx\_ODR or GPIOx\_BSRR Output

Hardware Abstraction Layer (HAL)

#define ADDR (\* ((volatile uintXX t \*) (0x40020000)))

Accessing a register

#define GPIOA MODER (\*((volatile uint32\_t \*)(0x40020000)))

- Each GPIO port has the same 10 registers

- There are 11 GPIO ports  $\rightarrow$  GPIOA GPIOK

| Base addresses                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Typedef for reg_gpio_t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Pointers to struct of ty<br>tectine GPIOR<br>tectine GPIOR | pe reg_gpio_t     (reg_gpio_t *) 0x40020000 )     (reg_gpio_t *) 0x40020400 )     (reg_gpio_t *) 0x40020400 )     (reg_gpio_t *) 0x40020400 )     (reg_gpio_t *) 0x4002000 )     (reg_gpio_t *) 0x4002100 )     (reg_gpio_t *) 0x4002200 )     (reg_gpio_t *) 0x4002200 )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | * Ubrief Representation of GFDO register.<br>• Described in reference manual p.265ff.<br>• volatile uint32 to MODER: /*** Fort mode register. */<br>• volatile uint32 to GENER: /*** Output type register. */<br>• volatile uint32 to GENER: /*** Output type register. */<br>• volatile uint32 to GENER: /*** Output type register. */<br>• volatile uint32 to GENER: /*** output data register. */<br>• volatile uint32 to GENER: /*** output data register. */<br>• volatile uint32 to GENER: /*** output data register. */<br>• volatile uint32 to GENER: /*** output data register. */<br>• volatile uint32 to GENER /*** output data register. */<br>• volatile uint32 to GENER /*** output data register. */<br>• volatile uint32 to GENER /*** output data register. */<br>• volatile uint32 to GENER /*** output contrasting in S.15. */ |  |

|                                                                                                                                                                                                                     | the set of | ) reg_gpio_t;<br>size of registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

# Serial Connection – Overview / SPI

| UART                                                                                                                                             | SPI                                                   | 12C                                      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------|--|

| serial ports (RS-232)                                                                                                                            | 4-wire bus                                            | 2-wire bus                               |  |

| TX, RX opt. control signals                                                                                                                      | MOSI, MISO, SCLK, SS                                  | SCL, SDA                                 |  |

| point-to-point                                                                                                                                   | point-to-multipoint                                   | (multi-) point-to-multi-point            |  |

| full-duplex                                                                                                                                      | full-duplex                                           | half-duplex                              |  |

| asynchronous                                                                                                                                     | synchronous                                           | synchronous                              |  |

| only higher layer addressing                                                                                                                     | slave selection through $\overline{\text{SS}}$ signal | 7/10-bit slave address                   |  |

| parity bit possible                                                                                                                              | no error detection                                    | no error detection                       |  |

| chip-to-chip, PC terminal program                                                                                                                | chip-to-chip, on-board connections                    | chip-to-chip, board-to-board connections |  |

| The three interfaces provide the lowest layer of communication and require higher level protocols to provide and interpret the transferred data. |                                                       |                                          |  |

I2C – Inter-Integrated Circuit

- Synchronous half-duplex transmission (SCL, SDA)

- 7-bit slave addresses

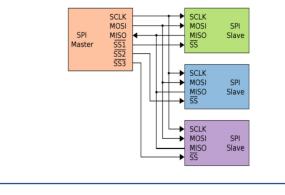

#### Single Master – Multiple Slaves

- Master generates a common clock signal for all slaves

- MOSI From Master Output to all Slave Inputs

- MISO All slave outputs connected to single master input

- Slaves

- Individual select <u>SS1</u>, <u>SS2</u>, <u>SS3</u>

- $\overline{SSx} = 1' \rightarrow \text{Slave output MISOx is tri-state}$

### UART - Asynchronous Serial Interface

- Transmitter and receiver use diverging clocks

- Synchronization using start/stop bits  $\rightarrow$  overhead

- Longer connections require line drivers  $\rightarrow$  RS-232/RS-485

### SPI – Serial Peripheral Interface

- Master / Slave

- Synchronous full-duplex transmission (MOSI, MISO)

- Selection of device through Slave Select (SS)

- No acknowledge, no error detection

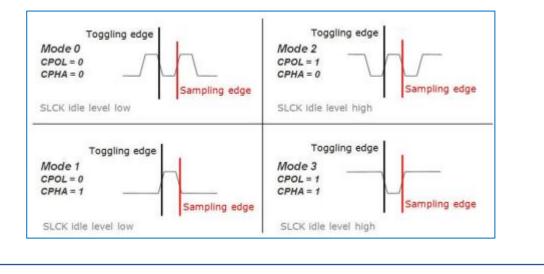

- Four mode  $\rightarrow$  clock polarity and clock phase

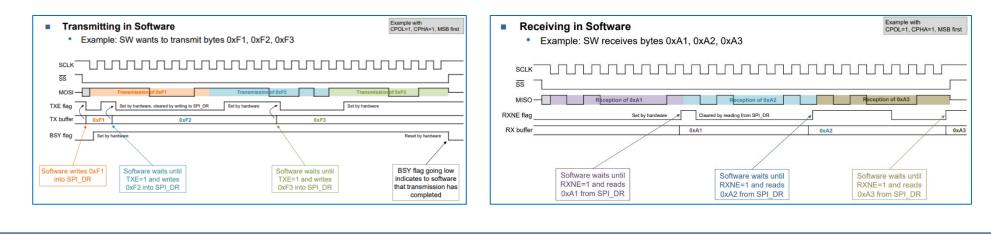

# Clock Polarity (CPOL) and Clock Phase (CPHA)

- TX provides data on 'Toggling Edge'

- RX takes over data with 'Sampling Edge'

# Serial Connection - SPI

Properties

### <u>Example</u>

- Use of  $\overline{SS}$  instead  $\rightarrow$  KISS

- Transmission without receive acknowledge and error detection

- Has to be implemented in higher level protocols

- Originally used only for transmission of single bytes

- *SS* deactivated after each byte

- Today also used for streams

- Data rate

- Highly flexible as clock signal is transmitted

- No flow-control available

- Master can delay the next clock edge

- Slave can't influence the data rate

- Susceptible to spikes on clock line

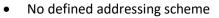

#### Synchronizing Hardware and Software

- TXE TX Buffer Empty Software can write next TX Byte to register SPI\_DR

- RXNE RX Buffer Not Empty A byte has been received. Software can read it from SPI\_DR

Ein Prozessor (SPI Master) sendet das Byte  $0x3D = 0011 \ 1101$ . Die Schnittstelle ist wie folgt konfiguriert:

Mode = 3, CPOL = 1, CPHA = 1, MSB - First

# UART / I2C – Universal Synchronous Receiver Transmitter / Inter-Integrated Circuit

V

RX shift registe

# Universal Asynchronous Receiver Transmitter – UART

Connecting shift registers with diverging clock sources

- Same target frequency

- Different tolerances and divider ratios

- Requires synchronization at start of each data item in receiver

# **UART Timing**

Transition stop ('1')  $\rightarrow$  start ('0')

- Receiver detects edge at the start of each data block (5 to 8 bits)

- Allows receiver to sample data «in middle of bits» → red edges

- Clocks have to be accurate enough to allow sampling up to parity bit

|      |         | 5 – 8 Bits of | Data (LSB first | :)                          |            |                                                                                                                                                                                |

|------|---------|---------------|-----------------|-----------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| idle | start 1 | 1 0 1         | 0 0             | 1 0 <mark>parity sto</mark> | op start 0 | $\begin{array}{rll} \mbox{Idle} & \rightarrow \mbox{Iogic} \ '1' \\ \mbox{stop} & \rightarrow \mbox{Iogic} \ '1' \\ \mbox{start} & \rightarrow \mbox{Iogic} \ '0' \end{array}$ |

|      | 1.5 * T |               |                 |                             | 1.5 * T    |                                                                                                                                                                                |

|      | тт      | ттт           | тт              | тттт                        | гт         |                                                                                                                                                                                |

# **UART Characteristics**

- Synchronization

- Each data item (5-8 bits) requires synchronization

- Asynchronous data transfer

- Mismatch of clock frequencies in TX and RX

- Requires overhead for synchronization → additional bits

- Requires effort for synchronization → additional hardware

- Advantage

- Clock does not have to be transmitted

- Transmission delays are automatically compensated

- On-board connections

- Signal levels are 3V or 5V with reference to ground

- Off-board connections require strong output drivers

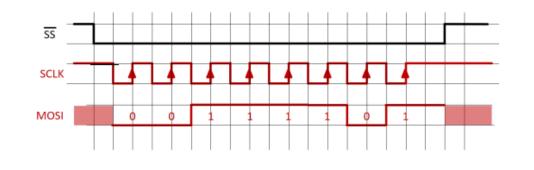

- I2C Bus I2C Inter-Integrated Circuit

- Bidirectional 2-wire

Clock → SCL Data → SDA

- Synchronous, half-duplex

- Each device on bus addressable

- 8-bit oriented data transfer

- Different bit rates up to 5 Mbit/s

- Suited for connection of multiple boards

- Multi-master possible

I2C Bus - Operation

- Master drives clock line (SCL)

- Master initiates / terminates transaction through START / STOP condition

**I2C Bus** – Driving Data on SDA

- Data driven onto SDA by master or by addressed slave

- Depending on transaction (read/write) and point in time

- Change of data only allowed when SCL is low

- Allow detection of START and STOP condition

I2C Bus – Data Transfer on I2C

- 8-bit oriented transfers

- Bit 9: Receiver acknowledges by driving SDA low

- Master defines number of 8-bit transfers (STOP)

Example: Ein Baustein soll zum lesen adressiert werden (7-Bit: 0x56)

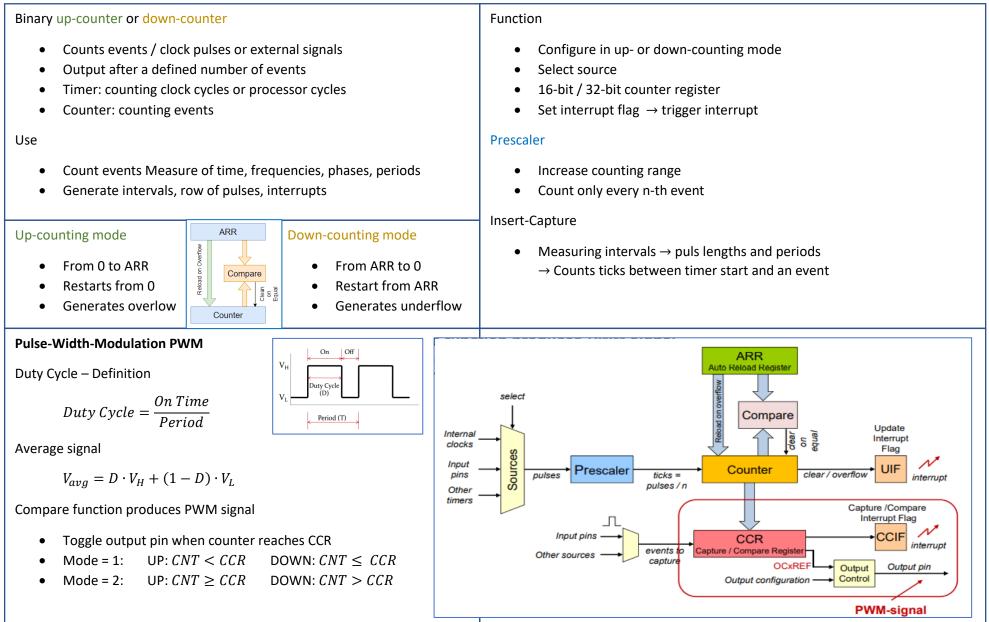

# Timer / Counter

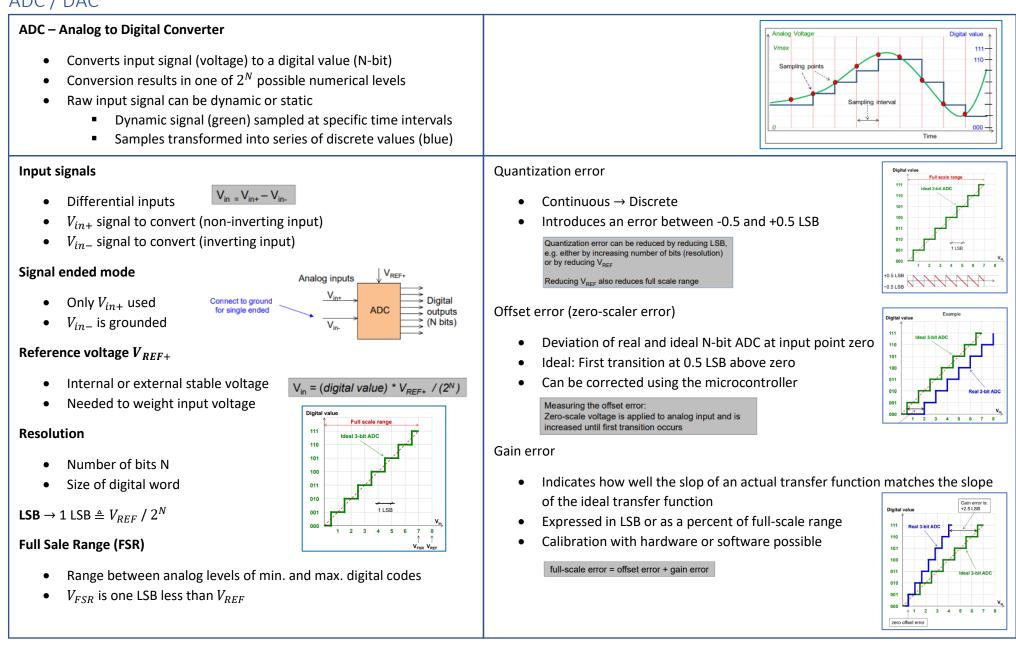

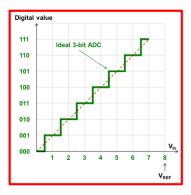

# ADC / DAC

# ADC / DAC

# DAC – Digital to Analog Converter

- Converts N-bit digital input to analog voltage level

- Music from your MP3 player is read and converted back to sound

- A series of different values in the digital domain leads to a series of steps in the analog domain.

- «Play-back» time depends on time between conversions

# Output signal Vout

- Analog output

- Unipolar (only positive)

- Bipolar (positive or negative)

- Conversion yields approximation of digital signal

# Reference voltage V<sub>REF</sub>

- Accurate reference voltage

- Needed to relate digital value to a voltage

# ADC Example 1

Ein externes analoges Signal soll digital abgetastet werden.

Bei einer maximalen Referenzspannung von  $V_{Ref} = 4.5$ V soll eine Abtast-Auflösung von mindestens 5mV erreicht werden.

Wie viele Bits werden mindestens für die Analog-Digital Wandlung benötigt.

$$\frac{4.5V}{0.005V} = 900, \qquad \log_2(900) = 9.8 \to 10 \text{ Bit}$$

# ADC Example 2

Gegeben ist ein 3-bit ADC. Die Referenzspannung  $V_{REF} = 8V$  festgelegt.

In welchem Spannungsbereich bewegt sich der Quantisierungsfehler?

$$1 LSB = \frac{V_{REF}}{2^N} = \frac{8V}{2^3} = 1V$$

Der Quantisierungsfehler beträgt  $\pm 0.5 \cdot LSB \rightarrow \pm 0.5V$

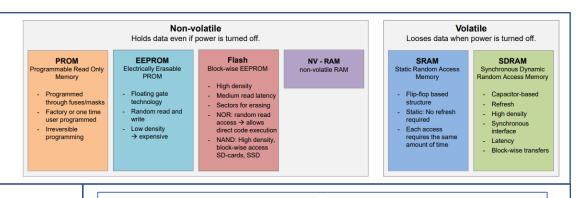

# Memory

# Übersicht

- PROM Programmable Read-Only Memory

- EEPROM Electrical Eraseable PROM

- NOR / NAN Flash

- SRAM Static Random Access Memory

- DRAM Dynamic Random Access Memory

| Static RAM (SRAM)                                                                                             | Synchronous Dynamic RAM (SDRAM)                                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Flip-flop/latch $\rightarrow$ 4 Transistors / 2 resistors                                                     | Transistor and capacitor                                                                                                                     |  |

| word line                                                                                                     | word line                                                                                                                                    |  |

| Large cell Low density, high cost Up to 64 Mb per device                                                      | Small cell <ul> <li>High density, low cost</li> <li>Up to 4 Gb per device</li> </ul>                                                         |  |

| Almost no static power consumption<br>• Static i.e. no accesses taking place                                  | Leakage currents<br>• Requires periodic refresh                                                                                              |  |

| Asynchronous interface (no clock) <ul> <li>Simple connection to bus</li> </ul>                                | Synchronous interface (clocked) <ul> <li>Requires dedicated SDRAM Controller</li> </ul>                                                      |  |

| All accesses take roughly the same time<br>• ~5ns per access → 200 MHz<br>• Suitable for distributed accesses | Long latency for first access of a block <ul> <li>Fast access for blocks of data (bursts)</li> <li>Large overhead for single byte</li> </ul> |  |

#### Write Operations (Programming)

- Can only change bits from '1' to '0'

Otherwise an erase operation is required

- · Word, half-word or byte access possible

- Writing a double word ~16 us

I.e. around 1000 times slower than SRAM

- Erase Operations

- Change all bits from '0' to '1'

- Only possible by sector or by bank, not on a word

- Typical sector sizes of 16

- Erase of a 128 Kbytes sector takes between 1 and 2 seconds <sup>1)</sup>

- Endurance: 10'000 erase cycles <sup>2)</sup>

- Sector may not be accessed (write or read) during erase

- I.e. execute program from another sector or from SRAM during erase

<sup>1)</sup> Depending on supply voltage and configuration parameters 2) Value from STM32F429ZI datasheet

|              | NOR Flash                                                                                                                       | NAND Flash                                                                                                                                                          |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Topology     |                                                                                                                                 |                                                                                                                                                                     |  |

| Applications | <ul> <li>Execute code directly from<br/>memory</li> <li>Persistent device configurations<br/>(replacement of EEPROM)</li> </ul> | <ul> <li>File-based IO, disks</li> <li>Large amounts of sequential data<br/>(images, SD cards, SSD)</li> <li>Load programs into RAM before<br/>executing</li> </ul> |  |

| Density      | Medium Up to 2 GBit = 256 MByte                                                                                                 | High Up to 1 Tbit                                                                                                                                                   |  |

| Interface    | <ul> <li>Read same as asynchronous SRAM</li> <li>Types with serial interface available</li> </ul>                               | Special NAND flash interface     Error correction for defective blocks                                                                                              |  |

| Access       | <ul> <li>Random access<br/>read ~0.12 µs</li> <li>Writing individual bytes possible</li> </ul>                                  | <ul> <li>Slow random access<br/>read: 1. Byte 25 µs,<br/>then 0.03 µs each</li> <li>Writing of individual bytes difficult</li> </ul>                                |  |

|              | <ul> <li>Slow writes</li> <li>~180 µs / 32 Byte</li> </ul>                                                                      | <ul> <li>Fast block write<br/>~300 µs / 2'112 Bytes</li> </ul>                                                                                                      |  |

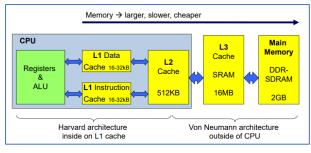

# Cache

# Definition

- Computer memory with short access time

- Storage of frequently / recently used instructions / data

# Principle of locality

- Spatial locality likely close to next accessed location ٠

- Temporal locality likely being accessed again in near future •

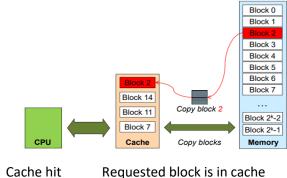

## Memory blocks

- Address range is partitioned into memory blocks

- Cache is guessing which blocks the CPU will need next

- Selected blocks copied to faster cache memory ٠

- Cache hit

- Cache miss Requested block is not in cache

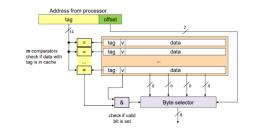

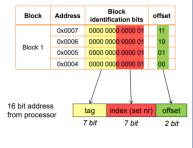

## **Organization -** Fully associative

- Tag contains complete block identification

- Any cache line can load any block

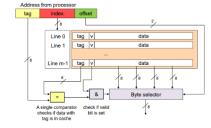

# **Organization - Direct mapped**

- Block identification split into tag and index •

- Each block is mapped to exactly one cache line

- Multiple memory blocks mapped to the same line

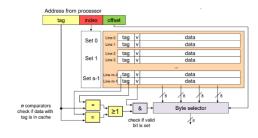

# Organization - N-way set associative

Partition into sets

# Cache

# Cache miss

- Cold miss first access to a block

- Capacity miss Working set larger than cache

- Conflict miss Multiple data objects map to same slot

## Performance

- Hit rate *hits / accesses*

- Miss rate misses / accesses = 1 hit rate

- Hit time Time to deliver a block from cache to processor

- Miss penalty Additional time to fetch from memory (miss)

# **Replacement Strategies**

- LRU Least recently used

- LFU Least frequently used

- FIFO First In-First-Out  $\rightarrow$  oldest

- Random randomly chosen

## Write Strategies (Hit)

- Write through immediately write to memory

- Write back write on before replacement (valid bit needed)

# Write Strategies (Miss)

- Write-allocate load line into cache and update line in cache

- No-write-allocate Write immediately to memory

| Organization   | Fully associative                                                                                                                                  | Direct mapped                                                                          | N-way set associative                                       |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| Number of sets | 1                                                                                                                                                  | m                                                                                      | m/n                                                         |  |

| Associativity  | m(=n)                                                                                                                                              | 1                                                                                      | n                                                           |  |

| Advantages     | <ul> <li>Fast, flexible</li> <li>Highest hit rates</li> <li>Advanced<br/>replacement<br/>strategies</li> </ul>                                     | <ul> <li>Simple logic</li> <li>Replacement strategy defined by organization</li> </ul> | Combination of both<br>other concepts                       |  |

| Disadvantages  | <ul> <li>Complex logic: one<br/>comparator per line</li> <li>Requires large area<br/>on silicon</li> <li>Replacement can be<br/>complex</li> </ul> | Lower hit rates                                                                        | to combine advantages<br>and to compensate<br>disadvantages |  |

# State Machines

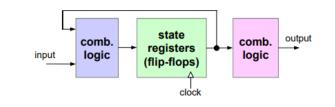

## FSM in Hardware

- Flip-flops store internal state

- Clock-driven

- Inputs are evaluated at each clock edge

- State can only change on a clock

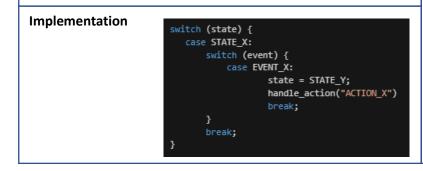

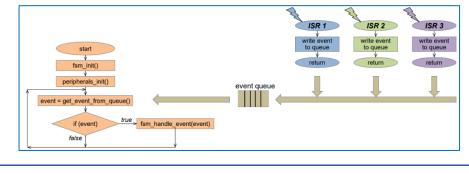

## FSM in Software

- Responds to external events

- Event driven

- Only evaluate the FSM if an input changes

- Internal state

- Memory of what happened before

- Actions

- Influence the outside world

- Each event may or may not

- change the internal state

- trigger actions

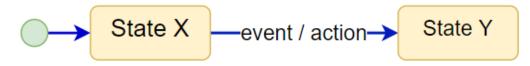

# **Modeling State Machines**

- State Internal state of the system in which it is awaiting the next event

- Transition Reaction to an event: May change state and/or trigger an action

- Event Asynchronous input that may cause a transition

- Action Output associated with transition

## **Rules for UML**

•

- Every state-diagram must have an *initial state*

- Each state must be *reachable* through a transition

- State diagram must be *deterministic*

# Semantics

- Only reacts to events from the outside

- Always has a defined state

- Reaction to an event depends on the current state

- Once started a transition cannot be interrupted

# **Events queues**

- Collect events generated by different objects

- FSM processes one event after another

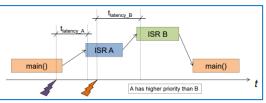

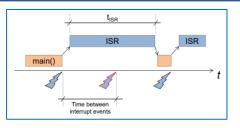

# Interrupt Performance

# Interrupt Performance

- $f_{INT}$  Interrupt frequency How often does an interrupt occur

- $t_{ISR}$  Interrupt service time Required time to process an interrupt

- $t_{ISR}$  > time between two interrupt events  $\rightarrow$  Some interrupts will be lost

- Percentage of CPU time used to service interrupts

### **Interrupt Latency**

Imp

- *t*<sub>latency</sub> Time between interrupt event and start of servicing by ISR

- Influenced by HW Instructions have different execution times

- Influenced by SW

$= f_{INT} \cdot t_{ISR}$

- Saving additional registers on stack...

- Interrupts with higher priority

- $f_{INT}$  too high  $\rightarrow$  Too many interrupts

- No CPU cycles left for data processing

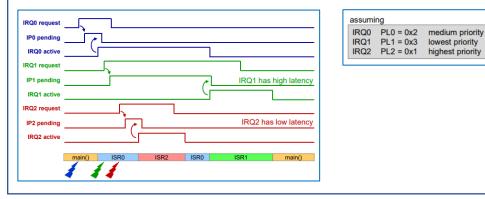

### **Example – Interrupt Priorities**

## Fast response times – low latency

- Fast CPU High clock rate / low number of cycles per instruction

- Extremely short polling loops can be fast

- Pre-emption with appropriate priorities

### Managing Latency

- High prio interrupts may cause high latencies for low prio interrupts

- Remedy: Move "waiting loop" to main program

- Move non-time-critical work from ISRs to main loop

# Polling

AdvantagesSimple and straightforward, Implicit synchronization,<br/>Deterministic, No additional interrupt logic requiredDisadvantagesBusy wait → wastes CPU time, Reduced throughput,<br/>Long reaction times