# Elementare logische Verknüpfungen

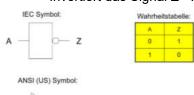

### Inverter (NOT-gate)

- Invertiert das Signal Z= !A

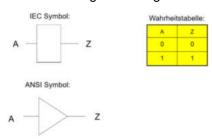

# <u>Puffer</u>

- Verzögert das Signal

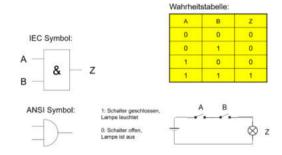

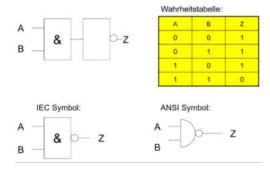

# AND-gate

- Für Ausgang Z= A&B

#### NAND-gate

- Für Ausgang Z= !(A&B)

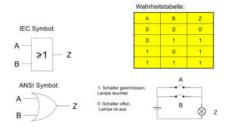

#### OR-gate

- Für Ausgang Z= A#B

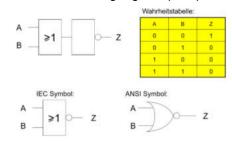

### NOR-gate

- Für Ausgang Z= !(A#B)

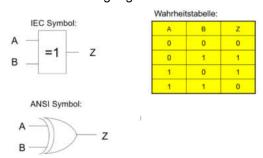

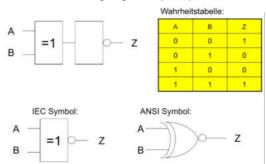

#### EXOR / XOR-gate

- Für Ausgang Z= A#B einzeln

# EXNOR / XNOR-gate

- Für Ausgang Z = !(A#B) einzeln

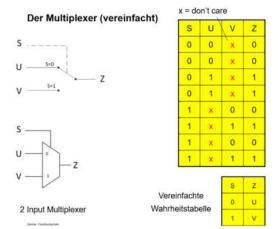

### Der Multiplexer (Muxer)

- S wählt zwischen U und V

| S | U | V | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

- Muxer können vereinfacht werden

#### **Boolsche Algebra**

OR-Vernüpfung: #

AND-Verknüpfung: &

NOT-Verknüpfung: !

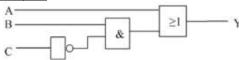

#### Beispiel:

Y= A # (B & !C)

#### Das Binär-/Hexadezimalsystem

| Dezimal | Binär | Hex |

|---------|-------|-----|

| 0       | 0000  | 0   |

| 1       | 0001  | 1   |

| 2       | 0010  | 2   |

| 3       | 0011  | 3   |

| 4       | 0100  | 4   |

| 5       | 0101  | 5   |

| 6       | 0110  | 6   |

| 7       | 0111  | 7   |

| 8       | 1000  | 8   |

| 9       | 1001  | 9   |

| 10      | 1010  | Α   |

| 11      | 1011  | b   |

| 12      | 1100  | С   |

| 13      | 1101  | d   |

| 14      | 1110  | E   |

| 15      | 1111  | F   |

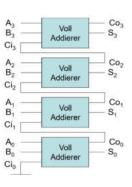

#### **Binärarithmetik**

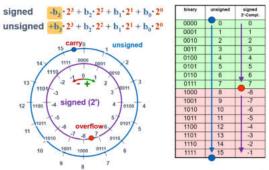

# Zweierkomplementzahlen (signed/ unsigned)

Negative Zahlen k\u00f6nnen dargestellt werden -> Achtung Over/Underflow!

Beispiel 4-Bit: Von 0 bis 7 und -8 bis -1

# 2-er Potenz-reihe

| Potenz      | Resultat |

|-------------|----------|

| 0           | 1        |

| 0 1 2 3     | 2        |

| 2           | 4        |

| 3           | 8        |

| 4           | 16       |

| 5           | 32       |

| 6           | 64       |

| 6<br>7<br>8 | 128      |

| 8           | 256      |

| 9           | 512      |

| 10          | 1024     |

| 11          | 2048     |

| 12          | 4096     |

| 13          | 8192     |

| 14          | 16'384   |

| 15          | 32'768   |

| 16          | 65'536   |

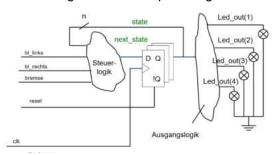

#### VHDL: Programmaufbau

- Eingangslogik

- Programm

- Ausgangslogik

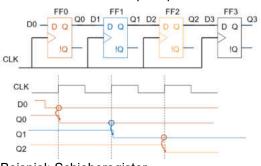

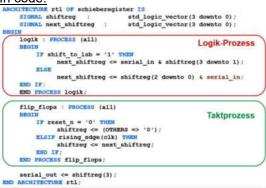

#### **VHDL: Schieberegister**

- Besteht aus Flip-Flops

#### Beispiel: Schieberegister

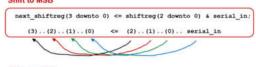

#### Shift to LSB

# In code:

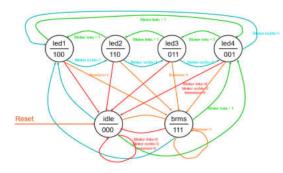

#### <u>Automaten - FSM (Finite State Machine)</u>

- Logikaufbau: Beispiel: Knight rider

#### Automaten: Bubble (RTL)-Diagramm

- Ermitteln der Zustände

- Ermitteln der Zustandsübergänge

- Zeichnen